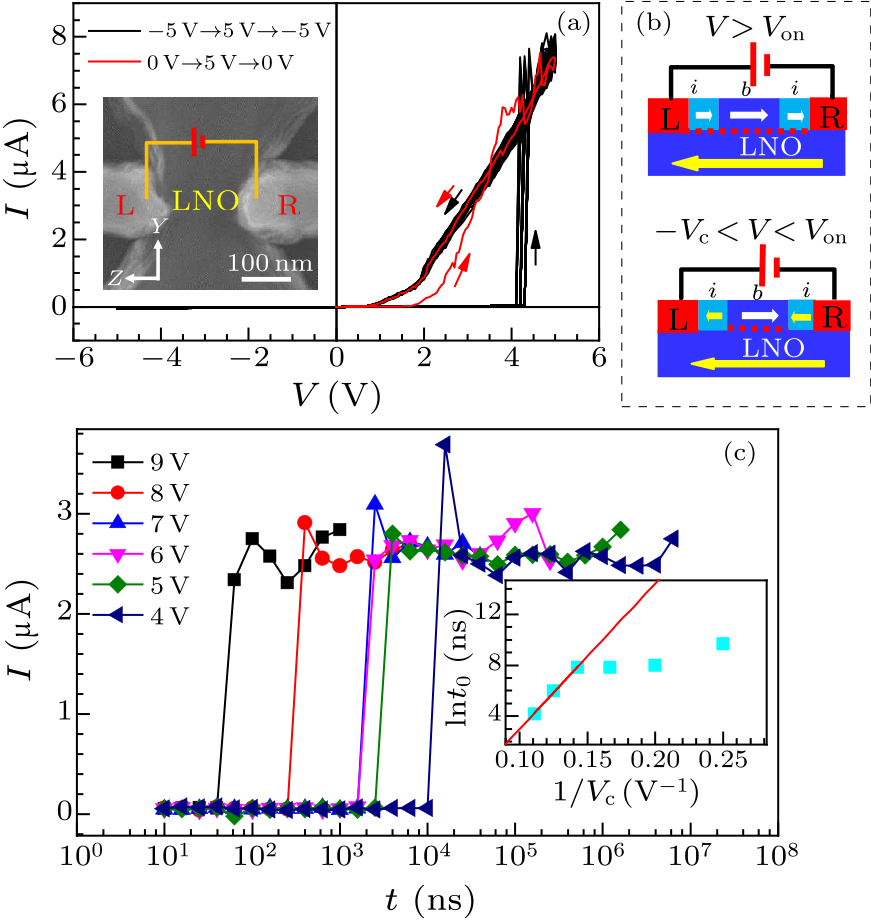

Fig. 1. (a) Double $I$–$V$ curves of 100 sweeps (black lines) between $-5$ V and 5 V for an LNO cell with dimensions of $w\times l\times h = 105\times 138\times 120$ nm$^{3}$. The red line shows the on-state $I$–$V$ curve after poling at 5 V, and the inset shows the SEM image of the cell in contact with L and R electrodes. The thin arrows indicate the voltage sweeping directions. (b) The orientations (thick arrows) of interfacial domains (${i}$) and inner domains (${b}$) under different applied voltages for the above LNO nanodevice after poling at 5 V, where the dotted lines show the DWs. (c) Switching time dependence of wall current at 3 V for different switching voltages, where the inset shows the ln$t_{0}$–$1/V$ plot, fitted by a solid line.

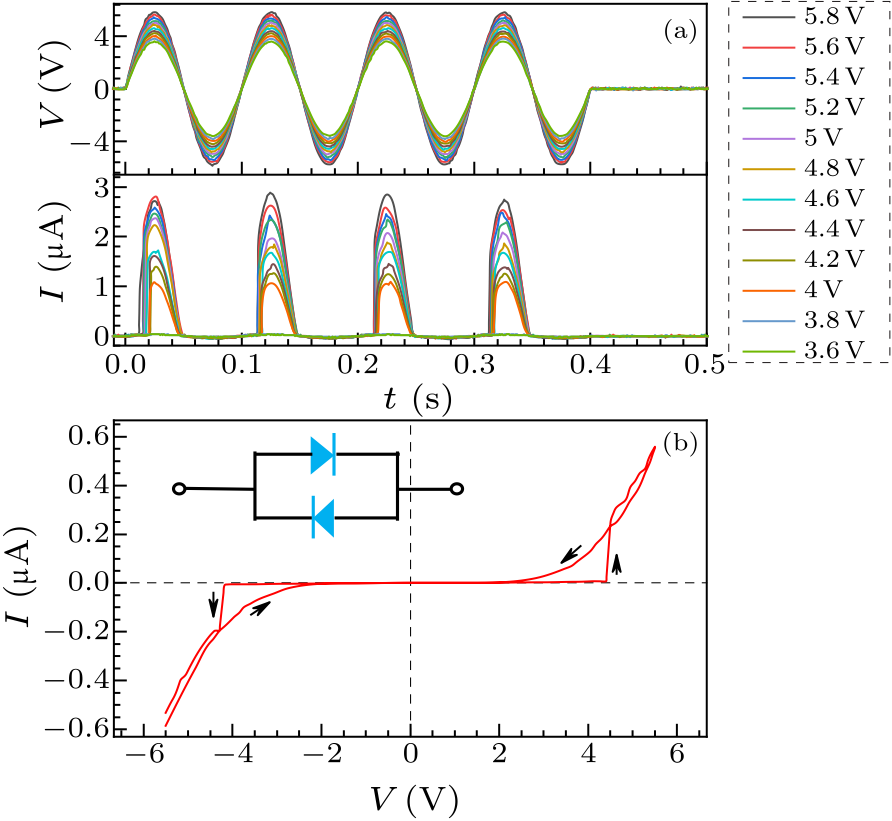

Fig. 2. (a) Output wall current transients (lower panel) from an LNO cell with dimensions of $w\times l\times h = 105\times 138\times 120$ nm$^{3}$, based on input sine waves at a frequency of 10 Hz at different amplitudes (upper panel). (b) The double $I$–$V$ curve for two identical LNO cells with dimensions of $w\times l\times h = 117\times 56\times 45$ nm$^{3}$, connected in opposite diode polarities, as shown by equivalent circuit diagram in the inset. The arrows indicate voltage sweeping directions.

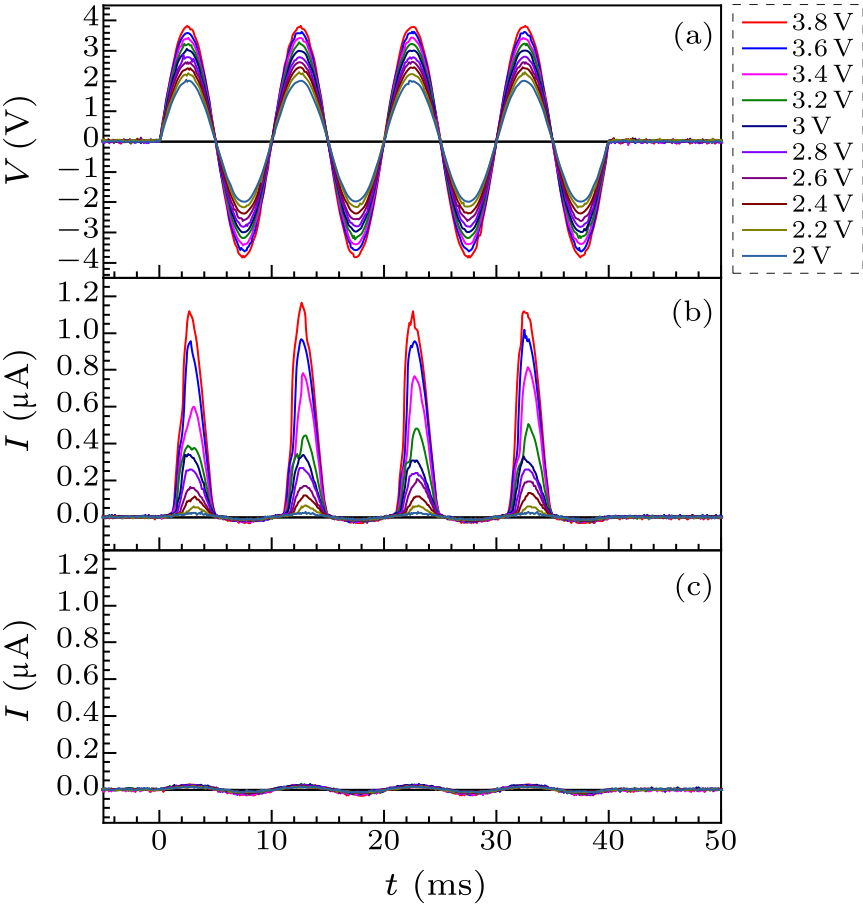

Fig. 3. (a) Input sine waves at a frequency of 100 Hz for different amplitudes. (b) Output wall current transients from an LNO cell with dimensions of $w\times l\times h = 105\times 138\times 120$ nm$^{3}$ after poling at 5 V. (c) Output wall current transients from the cell after poling at $-5$ V.

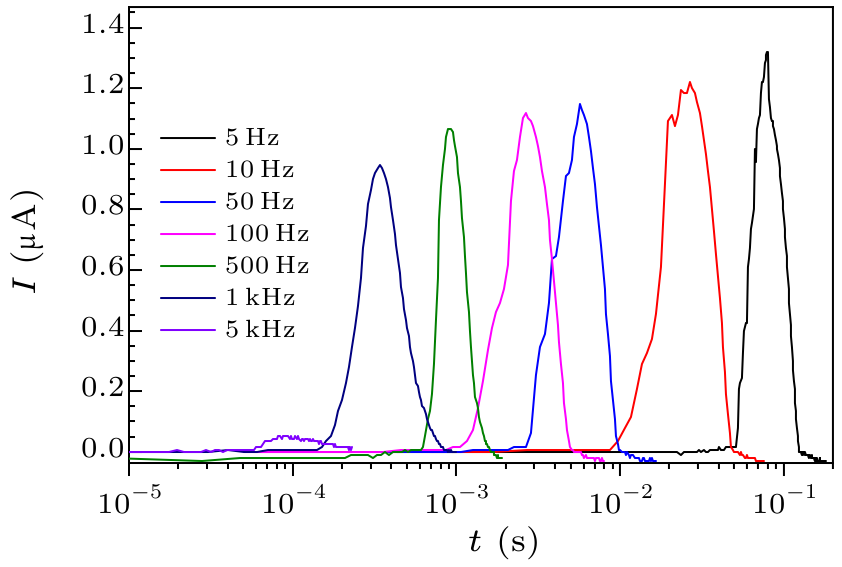

Fig. 4. (a) Output wall current transients at different frequencies for various input sine waves in amplitudes of 3.8 V from an LNO cell with dimensions of $w\times l\times h = 105\times 138\times 120$ nm$^{3}$ after poling at 5 V.

| [1] | Sharma P, Zhang Q, Sando D, Lei C H, Liu Y, Li J, Nagarajan V and Seidel J 2017 Sci. Adv. 3 e1700512 | Nonvolatile ferroelectric domain wall memory

| [2] | Jiang J, Bai Z L, Chen Z H, He L, Zhang D W, Zhang Q H, Shi J A, Park M H, Scott J F, Hwang C S and Jiang A Q 2018 Nat. Mater. 17 49 | Temporary formation of highly conducting domain walls for non-destructive read-out of ferroelectric domain-wall resistance switching memories

| [3] | Seidel J, Martin L W, He Q, Zhang Q, Chu Y H, Rother A, Hawkridge M E, Maksymovych P, Yu P, Gajek M, Balke N, Kalinin S V, Gemming S, Wang F, Catalan G, Scott J F, Spaldin N A, Orenstein J and Ramesh R 2009 Nat. Mater. 8 229 | Conduction at domain walls in oxide multiferroics

| [4] | Farokhipoor S and Noheda B 2011 Phys. Rev. Lett. 107 127601 | Conduction through 71° Domain Walls in Thin Films

| [5] | Crassous A, Sluka T, Tagantsev A K and Setter N 2015 Nat. Nanotechnol. 10 614 | Polarization charge as a reconfigurable quasi-dopant in ferroelectric thin films

| [6] | Wu W, Horibe Y, Lee N, Cheong S W and Guest J R 2012 Phys. Rev. Lett. 108 077203 | Conduction of Topologically Protected Charged Ferroelectric Domain Walls

| [7] | Meier D, Seidel J, Cano A, Delaney K, Kumagai Y, Mostovoy M, Spaldin N A, Ramesh R and Fiebig M 2012 Nat. Mater. 11 284 | Anisotropic conductance at improper ferroelectric domain walls

| [8] | Schröder M, Hau M A, Thiessen A, Soergel E, Woike T and Eng L M 2012 Adv. Funct. Mater. 22 3936 | Conducting Domain Walls in Lithium Niobate Single Crystals

| [9] | Godau C, Kämpfe T, Thiessen A, Eng L M and Haußmann A 2017 ACS Nano 11 4816 | Enhancing the Domain Wall Conductivity in Lithium Niobate Single Crystals

| [10] | Werner C S, Herr S J, Buse K, Sturman B, Soergel E, Razzaghi C and Breunig I 2017 Sci. Rep. 7 9862 | Large and accessible conductivity of charged domain walls in lithium niobate

| [11] | Sluka T, Tagantsev A K, Bednyakov P and Setter N 2013 Nat. Commun. 4 1808 | Free-electron gas at charged domain walls in insulating BaTiO3

| [12] | Volk T R, Gainutdinov R V and Zhang H H 2017 Appl. Phys. Lett. 110 132905 | Domain-wall conduction in AFM-written domain patterns in ion-sliced LiNbO 3 films

| [13] | Ma J, Zhang Q, Peng R, Wang J, Liu C, Wang M, Li N, Chen M, Cheng X, Gao P, Gu L, Chen L Q, Yu P, Zhang J and Nan C W 2018 Nat. Nanotechnol. 13 947 | Controllable conductive readout in self-assembled, topologically confined ferroelectric domain walls

| [14] | Bai Z L, Cheng X X, Chen D F, Zhang D W, Chen L Q, Scott J F, Hwang C S and Jiang A Q 2018 Adv. Funct. Mater. 28 1801725 | Hierarchical Domain Structure and Extremely Large Wall Current in Epitaxial BiFeO 3 Thin Films

| [15] | Stolichnov I, Iwanowska M, Colla E, Ziegler B, Gaponenko I, Paruch P, Huijben M, Rijnders G and Setter N 2014 Appl. Phys. Lett. 104 132902 | Persistent conductive footprints of 109° domain walls in bismuth ferrite films

| [16] | Rojac T, Bencan A, Drazic G, Sakamoto N, Ursic H, Jancar B, Tavcar G, Makarovic M, Walker J, Malic B and Damjanovic D 2017 Nat. Mater. 16 322 | Domain-wall conduction in ferroelectric BiFeO3 controlled by accumulation of charged defects

| [17] | Liu L, Xu K, Li Q, Daniels J, Zhou H, Li J, Zhu J, Seidel J and Li J F 2020 Adv. Funct. Mater. 2005876 | Giant Domain Wall Conductivity in Self‐Assembled BiFeO 3 Nanocrystals

| [18] | Jiang A Q, Geng W P, Lv P, Hong J W, Jiang J, Wang C, Chai X J, Lian J W, Zhang Y, Huang R, Zhang D W, Scott J F and Hwang C S 2020 Nat. Mater. 19 1188 | Ferroelectric domain wall memory with embedded selector realized in LiNbO3 single crystals integrated on Si wafers

| [19] | Wang C, Jiang J, Chai X, Lian J, Hu X and Jiang A Q 2020 ACS Appl. Mater. & Interfaces 12 44998 | Energy-Efficient Ferroelectric Domain Wall Memory with Controlled Domain Switching Dynamics

| [20] | Yoon K J, Kim G H, Yoo S, Bae W, Yoon J H, Park T H, Kwon D E, Kwon Y J, Kim H J and Kim Y M 2017 Adv. Electron. Mater. 3 1700152 | Double-Layer-Stacked One Diode-One Resistive Switching Memory Crossbar Array with an Extremely High Rectification Ratio of 10 9

| [21] | Wang G, Lauchner A C, Lin J, Natelson D, Palem K V and Tour J M 2013 Adv. Mater. 25 4789 | High-Performance and Low-Power Rewritable SiO x 1 kbit One Diode-One Resistor Crossbar Memory Array

| [22] | Chai X J, Jiang J, Zhang Q H, Hou X, Meng F Q, Wang J, Gu L, Zhang D W and Jiang A Q 2020 Nat. Commun. 11 2811 | Nonvolatile ferroelectric field-effect transistors

| [23] | Wang Z R, Wu H Q, Burr G W, Hwang C S, Wang K L, Xia Q F and Yang J J 2020 Nat. Rev. Mater. 5 173 | Resistive switching materials for information processing

| [24] | R, D S, Kawayama I, Mavani K, Takahashi K, Murakami H and Tonouchi M 2009 Adv. Mater. 21 2881 | Understanding the Nature of Ultrafast Polarization Dynamics of Ferroelectric Memory in the Multiferroic BiFeO 3

| [25] | Tselev A, Yu P, Cao Y, Dedon L R, Martin L W, Kalinin S V and Maksymovych P 2016 Nat. Commun. 7 11630 | Microwave a.c. conductivity of domain walls in ferroelectric thin films