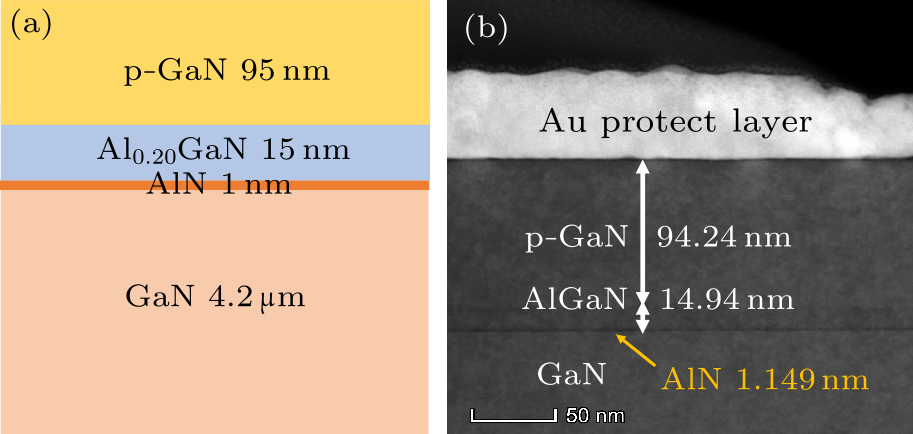

Fig. 1. (a) Schematic cross sections and (b) STEM image of the top epitaxy layers of p-GaN/AlGaN wafer.

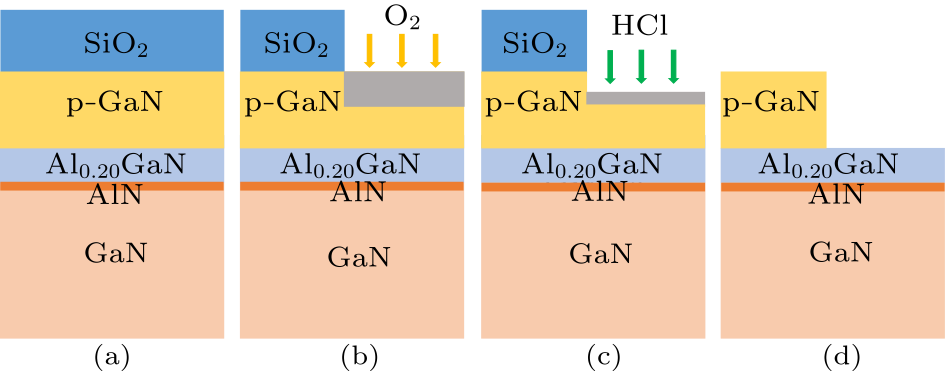

Fig. 2. Schematic diagrams showing the cross sections of the epitaxy structure during the whole etching process: (a) SiO$_{2}$ deposition as hard mask, (b) ICP plasma oxidation, (c) HCl wet etching, (d) SiO$_{2}$ hard mask removal after p-GaN etching.

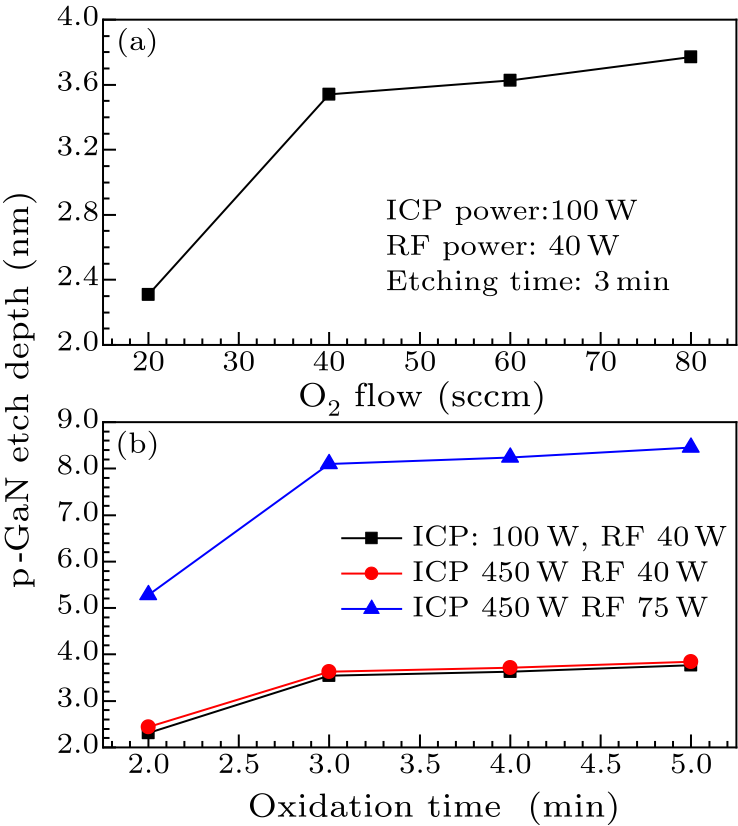

Fig. 3. (a) Characteristics of p-GaN etch depth under different O$_{2}$ flow, (b) p-GaN etch depth under different ICP power and rf power at 40 sccm O$_{2}$ flow.

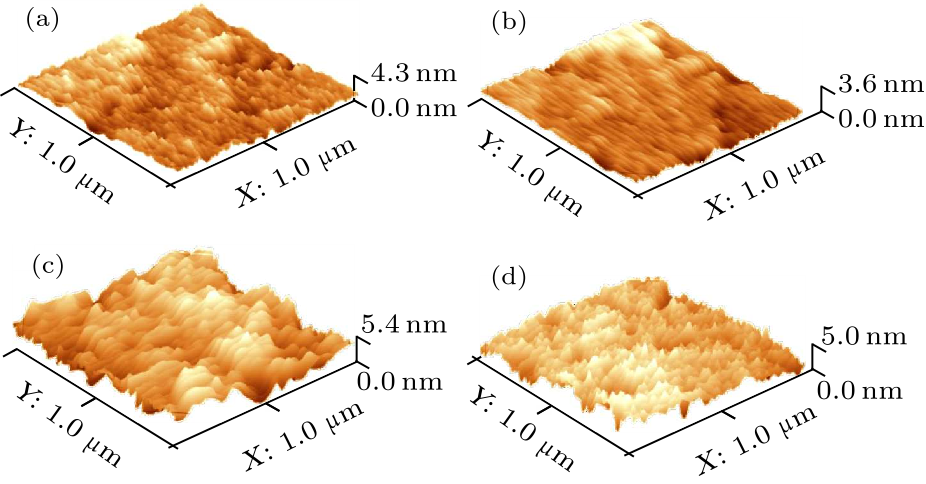

Fig. 4. AFM images of p-GaN surface: (a) as-grown, (b) after one circle digital etching, (c) after Cl$_{2}$/Ar/O$_{2}$ etching, (d) after BCl$_{3}$/SF$_{6}$ etching.

| Etching method | rms roughness | Mean roughness |

|---|---|---|

| (nm) | (nm) | |

| As grown | 0.499 | 0.383 |

| Digital etching | 0.452 | 0.351 |

| Cl$_{2}$/Ar/O$_{2}$ etching | 0.529 | 0.406 |

| BCl$_{3}$/SF$_{6}$ etching | 0.573 | 0.436 |

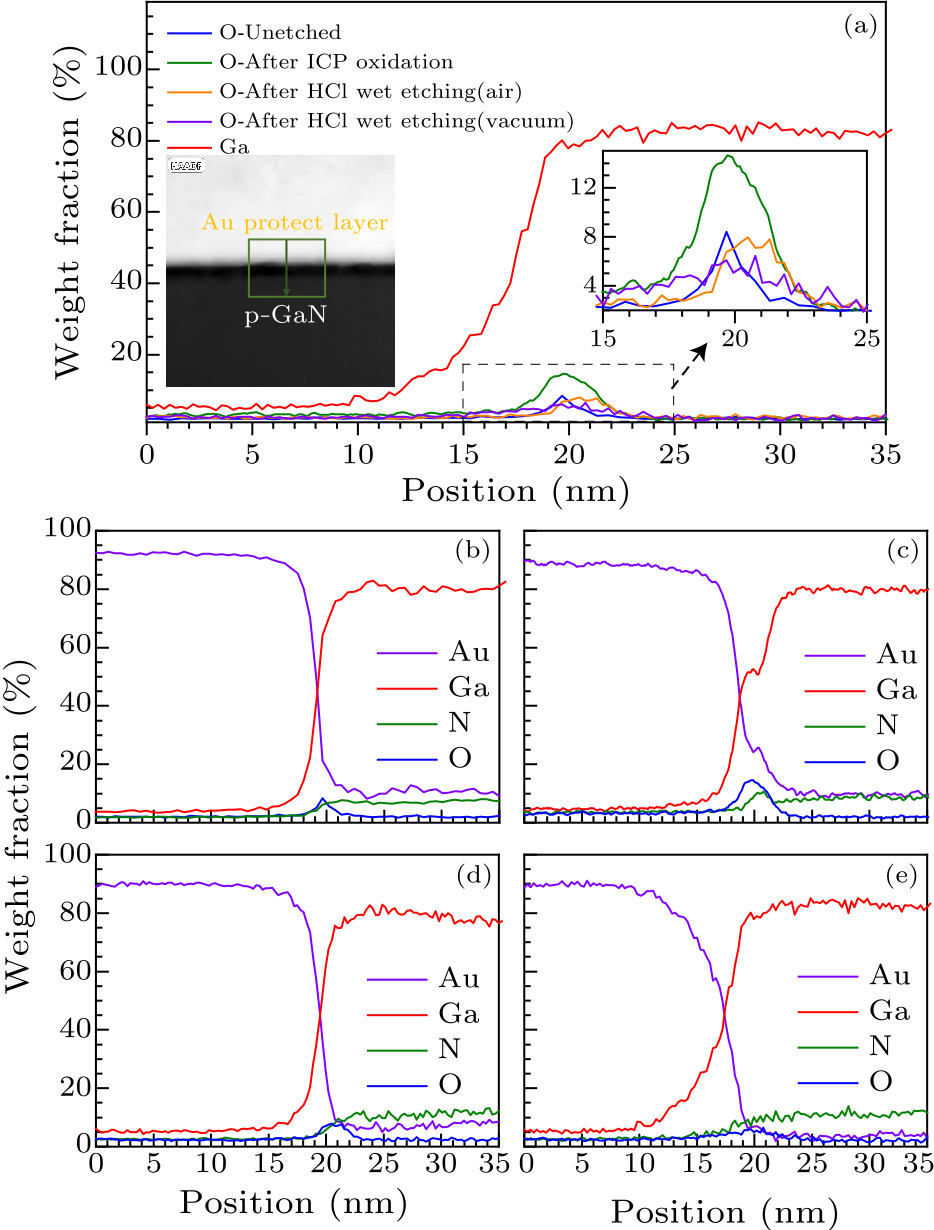

Fig. 5. The EDX analysis in the Au/p-GaN interface (a) O$_{2}$ weight fraction variation during whole process, STEM image showing EDX line scan area (green box and arrow), (b) as-grown and exposed in air, (c) after ICP plasma oxidation, (d) after ICP plasma oxidation, followed by HCl wet etching and exposed to air, (e) after ICP plasma oxidation, followed by HCl wet etching and sealing in vacuum.

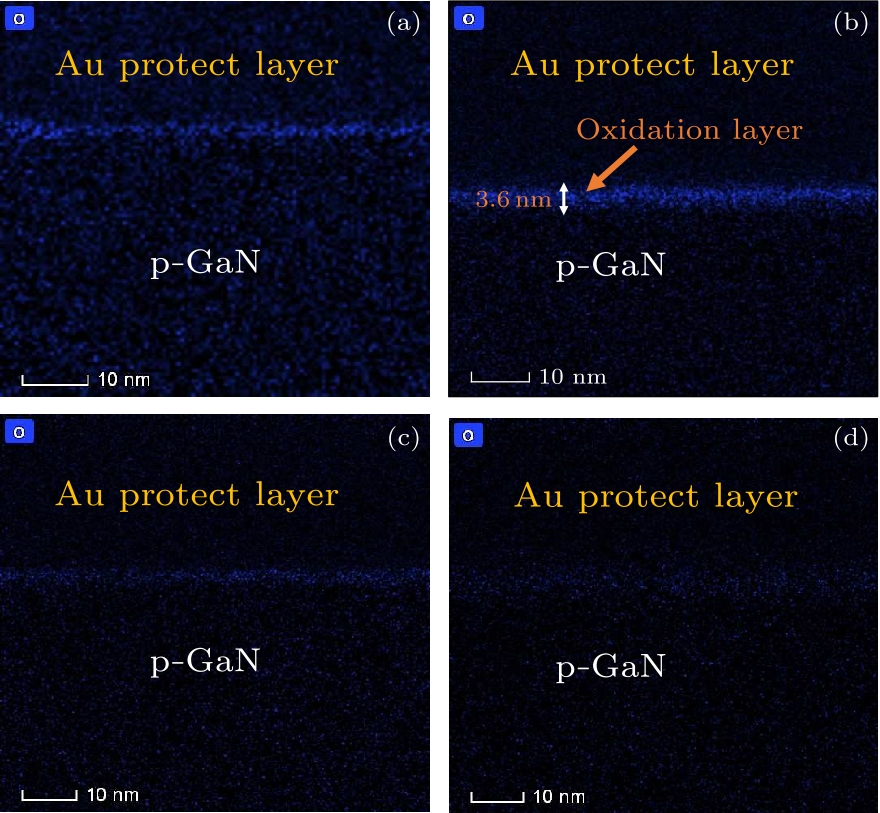

Fig. 6. STEM/EDX mapping showing O$_2$ element distribution at p-GaN surface: (a) as-grown and exposed in air, (b) after ICP plasma oxidation, (c) after ICP plasma oxidation, followed by HCl wet etching and exposed to air, (d) after ICP plasma oxidation, followed by HCl wet etching and sealing in vacuum.

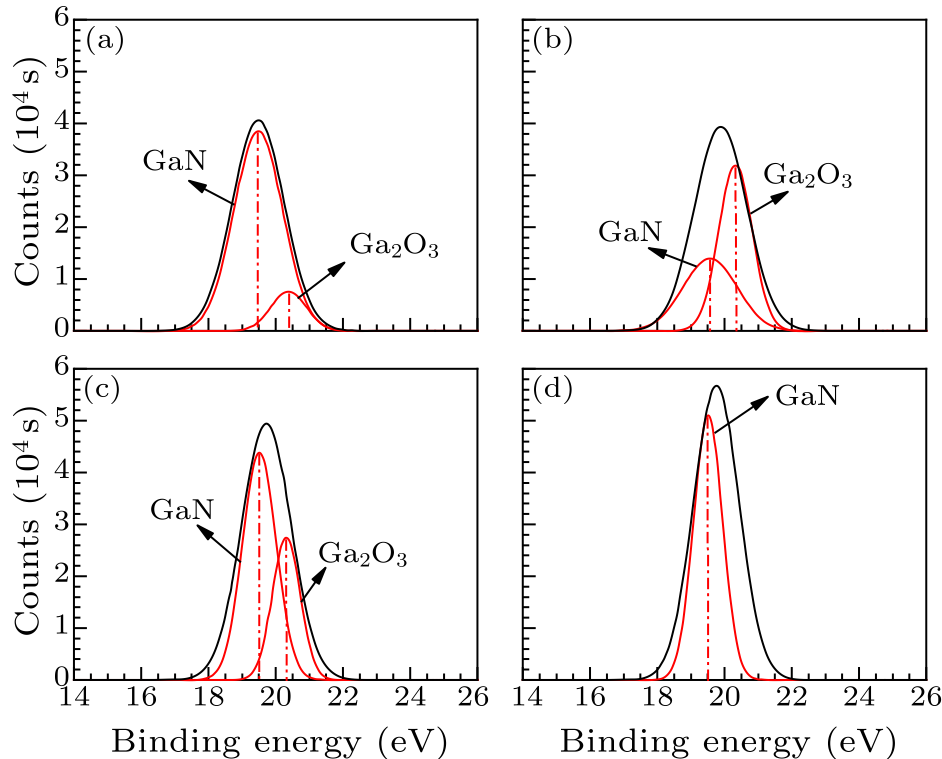

Fig. 7. XPS measurements of samples: (a) as-grown and exposed in air, (b) after ICP plasma oxidation, (c) after ICP plasma oxidation, followed by HCl wet etching and exposed to air, (d) after ICP plasma oxidation, followed by HCl wet etching and sealing in vacuum.

| [1] | Yusuke K, Keisuke U, Taketomo S, Tamotsu H et al 2017 J. Appl. Phys. 121 184501 | Precise thickness control in recess etching of AlGaN/GaN hetero-structure using photocarrier-regulated electrochemical process

| [2] | Chen K, Zhou C et al 2011 Phys. Status Solidi A 208 434 | Enhancement-mode AlGaN/GaN HEMT and MIS-HEMT technology

| [3] | Chen C, Keller S, Haberer E, Zhang L, Hu S E, Mishra U, Wu Y et al 1999 J. Vac. Sci. & Technol. B 17 2755 | Cl[sub 2] reactive ion etching for gate recessing of AlGaN/GaN field-effect transistors

| [4] | Buttari D et al 2003 Appl. Phys. Lett. 83 4779 | Origin of etch delay time in Cl2 dry etching of AlGaN/GaN structures

| [5] | Oka T et al 2008 IEEE Electron Device Lett. 29 668 | AlGaN/GaN Recessed MIS-Gate HFET With High-Threshold-Voltage Normally-Off Operation for Power Electronics Applications

| [6] | Wang Y H et al 2015 IEEE Electron Device Lett. 36 381 | 6.5 V High Threshold Voltage AlGaN/GaN Power Metal-Insulator-Semiconductor High Electron Mobility Transistor Using Multilayer Fluorinated Gate Stack

| [7] | Baharin A et al 2010 Conference on Optoelectronic and Microelectronic Materials and Devices (Canberra, ACT, Australia 12–15 December 2010) p 145 | Effect of very low power inductively coupled plasma etching on ohmic contacts to p-GaN

| [8] | Chen K J et al 2017 IEEE Trans. Electron Devices 64 779 | GaN-on-Si Power Technology: Devices and Applications

| [9] | Ge M, Cai Q, Zhang B H et al 2019 Chin. Phys. B 28 107301 | Negative transconductance effect in p-GaN gate AlGaN/GaN HEMTs by traps in unintentionally doped GaN buffer layer

| [10] | Basu A, Kumar V, Adesida I et al 2007 J. Vac. Sci. & Technol. B 25 2607 | Study of fluorine bombardment on the electrical properties of AlGaN∕GaN heterostructures

| [11] | Yi C W, Wang R N, Huang W et al 2007 IEEE International Electron Devices Meeting (Washington DC, USA 10–12 December 2007) p 389 | Reliability of Enhancement-mode AlGaN/GaN HEMTs Fabricated by Fluorine Plasma Treatment

| [12] | Lv L, Gong X, Hao Y et al 2008 Acta Phys. Sin. 57 1128 (in Chinese) | Properties of p-type GaN etched by inductively coupled plasma and their improvement

| [13] | Chiu H C et al 2018 IEEE Trans. Electron Devices 65 4820 | High Uniformity Normally-OFF p-GaN Gate HEMT Using Self-Terminated Digital Etching Technique

| [14] | Hahn H, Lükens G, Ketteniss N et al 2011 Appl. Phys. Express 4 114102 | Recessed-Gate Enhancement-Mode AlGaN/GaN Heterostructure Field-Effect Transistors on Si with Record DC Performance

| [15] | Zhou Y, Zhong Y Z, Gao H W et al 2017 IEEE J. Electron Devices Soc. 5 340 | p-GaN Gate Enhancement-Mode HEMT Through a High Tolerance Self-Terminated Etching Process

| [16] | Buttari D, Chini A, Chakraborty A, Mishra U K et al 2004 Int. J. High Speed Electron. Syst. 14 756 | SELECTIVE DRY ETCHING OF GaN OVER AlGaN IN BCL 3 / SF 6 MIXTURES

| [17] | Buttari D, Heikman S, Keller S et al 2002 IEEE Lester Eastman Conference on High Performance Devices (Newark, DE, USA 6–8 August 2002) p 461 | Digital etching for highly reproducible low damage gate recessing on AlGaN/GaN HEMTs

| [18] | Burnham S, Boutros K, Hashimoto P, Butler C, Wong D, Hu M, Micovic M et al 2010 Phys. Status Solidi C 7 2010 | Gate-recessed normally-off GaN-on- Si HEMT using a new O2-BCl3 digital etching technique

| [19] | Chiu H C, Yang C W, Chen C H, Fu J S, Chen F T et al 2011 Appl. Phys. Lett. 99 153508 | Characterization of enhancement-mode AlGaN/GaN high electron mobility transistor using N 2 O plasma oxidation technology

| [20] | Sokolovskij R, Sun J, Santagata F, Iervolino E, Li S, Zhang G Y, Sarro P M, Zhang G Q et al 2016 Procedia Eng. 168 1094 | Precision Recess of AlGaN/GaN with Controllable Etching Rate Using ICP-RIE Oxidation and Wet Etching