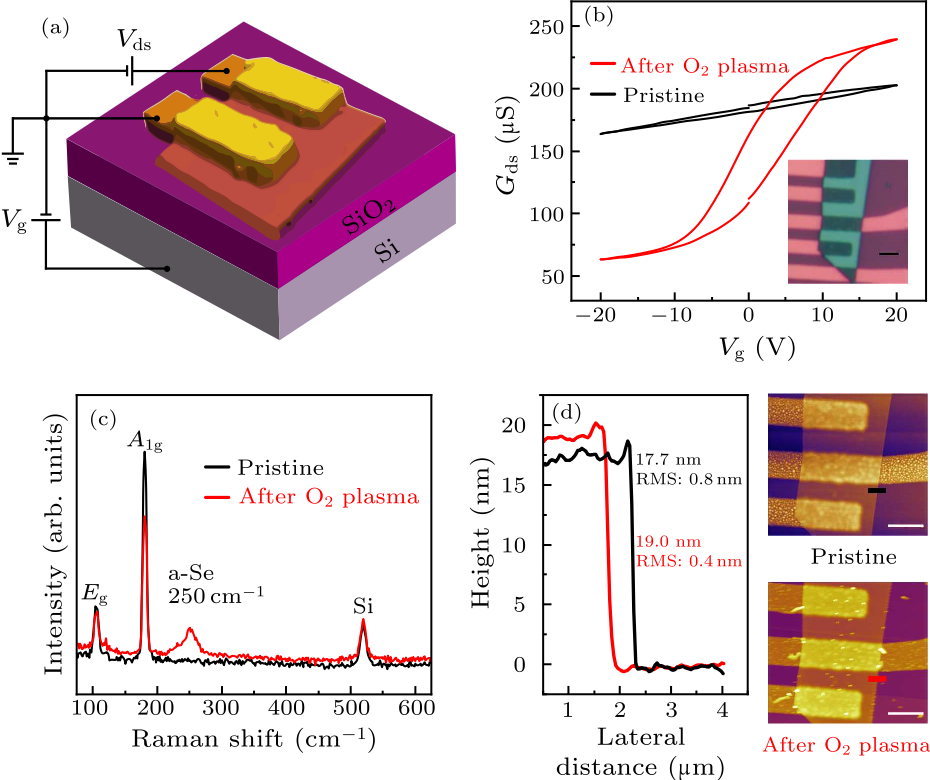

Fig. 1. Basic characterizations of the SnSe$_{2}$ FETs before and after plasma treatment. (a) Schematic of the SnSe$_{2}$ thin flake FET device. (b) Conductance versus gate voltage for a typical SnSe$_{2}$ FET device in air before (black) and after (red) oxygen plasma treatment. Inset: the optical microscope image of the device. The scale bar is 10 µm. (c) Raman spectra of a SnSe$_{2}$ flake before (black) and after (red) oxygen plasma treatment. (d) AFM measurements before (black) and after (red) oxygen plasma treatment of the device shown in (b). The scale bars are 10 µm.

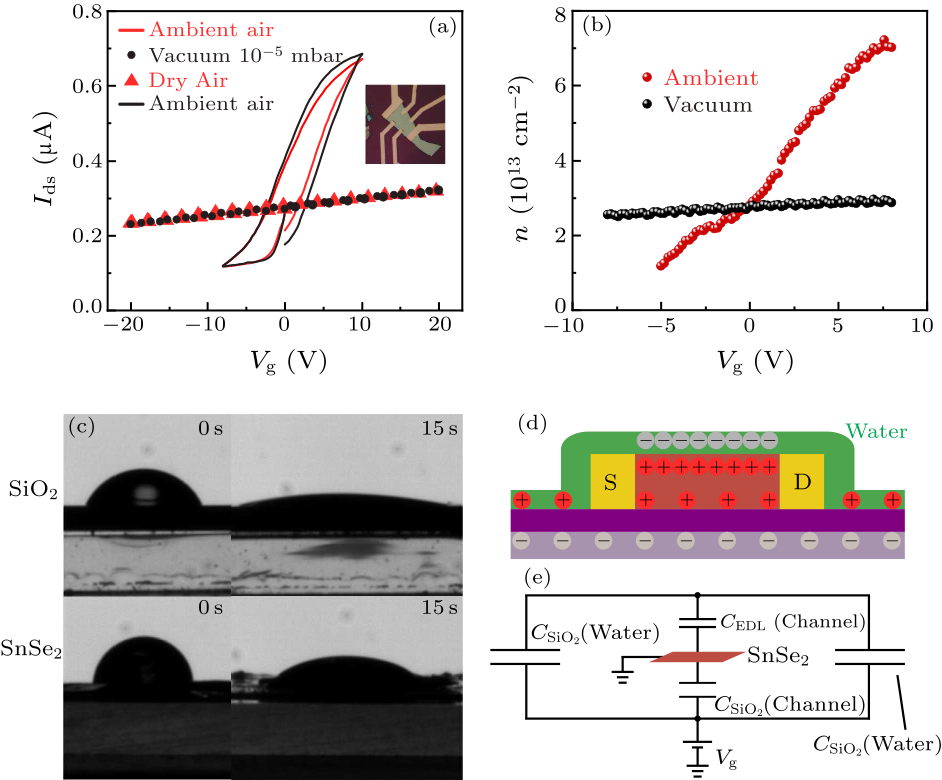

Fig. 2. Unveiling the mechanism of greatly enhanced coupling between the gate and channel. (a) Transfer measurements under different conditions showing the important role of water. The relative humidity of ambient air is 60%. The inset shows the optical microscope image of the device. (b) Hall measurements of the carrier density as a function of gate voltage under vacuum and ambient conditions. (c) Water contact angles, indicating that the hydrophilicity has increased for both SiO$_{2}$ and SnSe$_{2}$ after O$_{2}$ plasma treatment. (d) The model to explain the greatly enhanced capacitive coupling between the back gate and the channel. A water film (green colored layer) is formed on the whole sample to act as an ion liquid. (e) The equivalent capacitance circuit to calculate the effective capacitive coupling between the gate and the channel.

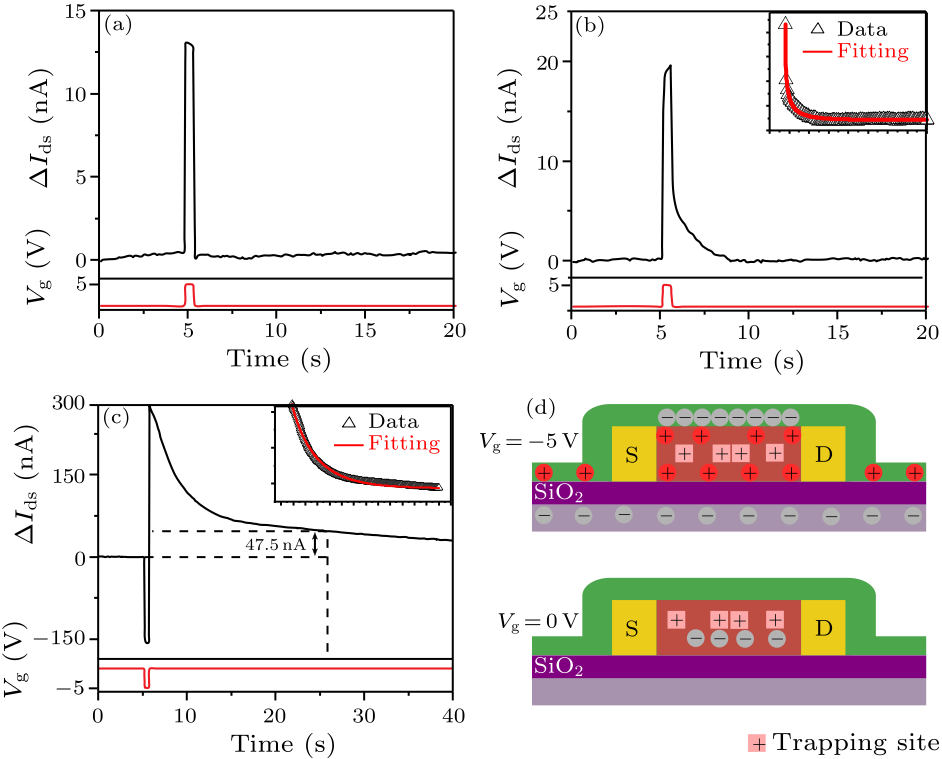

Fig. 3. Effects of short- and long-term memories of plasma-treated FETs. (a) Relative channel current ($\Delta I_{\rm ds}$) in response to a gate pulse, before plasma treatment, and (b) $\Delta I_{\rm ds}$ in response to a gate pulse after plasma treatment, showing short-term memory. Inset: stretched exponential decay fitting to the data in the main panel with a retention time of 0.18 s. (c) Long-term memory is achieved by applying a negative gate pulse to a plasma treated SnSe$_{2}$ FET. The dashed lines show that at 20 s after the pulse, $\Delta I_{\rm ds}\approx 47.5$ nA. Inset: stretched exponential decay fitting to the data in the main panel with a retention time of 4 s. (d) Model to explain the long-term memory. The channel contains hole trap sites represented by the squares with a $+$ sign, while circles with either $+$ or $-$ sign are mobile charge carriers (ions in the water film and holes or electrons in the channel).

| [1] | He D, Zhang Y, Wu Q et al 2014 Nat. Commun. 5 5162 | Two-dimensional quasi-freestanding molecular crystals for high-performance organic field-effect transistors

| [2] | Zhang W L 2019 Chin. Phys. Lett. 36 067301 | Improvement of Performance of HfS 2 Transistors Using a Self-Assembled Monolayer as Gate Dielectric

| [3] | Xiang D, Han C, Wu J et al 2015 Nat. Commun. 6 6485 | Surface transfer doping induced effective modulation on ambipolar characteristics of few-layer black phosphorus

| [4] | Chen M, Nam H, Wi S et al 2013 Appl. Phys. Lett. 103 142110 | Stable few-layer MoS 2 rectifying diodes formed by plasma-assisted doping

| [5] | Han C, Hu Z, Gomes L C et al 2017 Nano Lett. 17 4122 | Surface Functionalization of Black Phosphorus via Potassium toward High-Performance Complementary Devices

| [6] | Liu Y L, Nan H Y, Wu X et al 2013 ACS Nano 7 4202 | Layer-by-Layer Thinning of MoS 2 by Plasma

| [7] | Shim J, Oh A, Kang D H et al 2016 Adv. Mater. 28 6985 | High-Performance 2D Rhenium Disulfide (ReS 2 ) Transistors and Photodetectors by Oxygen Plasma Treatment

| [8] | Jia J, Jang S K, Lai S et al 2015 ACS Nano 9 8729 | Plasma-Treated Thickness-Controlled Two-Dimensional Black Phosphorus and Its Electronic Transport Properties

| [9] | Zhu J Q, Wang Z C, Yu H et al 2017 J. Am. Chem. Soc. 139 10216 | Argon Plasma Induced Phase Transition in Monolayer MoS 2

| [10] | Pei J J, Gai X, Yang J et al 2016 Nat. Commun. 7 10450 | Producing air-stable monolayers of phosphorene and their defect engineering

| [11] | Pei T, Bao L, Wang G et al 2016 Appl. Phys. Lett. 108 053506 | Few-layer SnSe 2 transistors with high on/off ratios

| [12] | Guo C L, Tian Z, Xiao Y J et al 2016 Appl. Phys. Lett. 109 203104 | Field-effect transistors of high-mobility few-layer SnSe 2

| [13] | Tosun M, Chan L, Amani M et al 2016 ACS Nano 10 6853 | Air-Stable n-Doping of WSe 2 by Anion Vacancy Formation with Mild Plasma Treatment

| [14] | Choudhary N, Islam M R, Kang N et al 2016 J. Phys.: Condens. Matter 28 364002 | Two-dimensional lateral heterojunction through bandgap engineering of MoS 2 via oxygen plasma

| [15] | Islam M R, Kang N, Bhanu U et al 2014 Nanoscale 6 10033 | Tuning the electrical property via defect engineering of single layer MoS 2 by oxygen plasma

| [16] | Lioi D B, Gosztola D J, Wiederrecht G P et al 2017 Appl. Phys. Lett. 110 081901 | Photon-induced selenium migration in TiSe 2

| [17] | Kim B J, Jang H, Lee S K et al 2010 Nano Lett. 10 3464 | High-Performance Flexible Graphene Field Effect Transistors with Ion Gel Gate Dielectrics

| [18] | Pu J, Yomogida Y, Liu K K et al 2012 Nano Lett. 12 4013 | Highly Flexible MoS 2 Thin-Film Transistors with Ion Gel Dielectrics

| [19] | Perera M M, Lin M W, Chuang H J et al 2013 ACS Nano 7 4449 | Improved Carrier Mobility in Few-Layer MoS 2 Field-Effect Transistors with Ionic-Liquid Gating

| [20] | Zhao S Y F, Elbaz G A, Bediako D K et al 2018 Nano Lett. 18 460 | Controlled Electrochemical Intercalation of Graphene/ h- BN van der Waals Heterostructures

| [21] | Ji H, Wei J and Natelson D 2012 Nano Lett. 12 2988 | Modulation of the Electrical Properties of VO 2 Nanobeams Using an Ionic Liquid as a Gating Medium

| [22] | Panzer M J, Newman C R and Frisbie C D 2005 Appl. Phys. Lett. 86 103503 | Low-voltage operation of a pentacene field-effect transistor with a polymer electrolyte gate dielectric

| [23] | Huang Y, Sutter E, Wu L M et al 2018 ACS Appl. Mater. Interfaces 10 23198 | Thick Layered Semiconductor Devices with Water Top-Gates: High On–Off Ratio Field-Effect Transistors and Aqueous Sensors

| [24] | Smith A J, Owens S and Forsythe I D 2000 J. Physiol. 529 681 | Immunocytochemical evidence for inhibitory and disinhibitory circuits in the superior olive

| [25] | Zhu L Q, Wan C J, Guo L Q et al 2014 Nat. Commun. 5 3158 | Artificial synapse network on inorganic proton conductor for neuromorphic systems

| [26] | Chang T, Jo S H and Lu W 2011 ACS Nano 5 7669 | Short-Term Memory to Long-Term Memory Transition in a Nanoscale Memristor

| [27] | Sturman B, Podivilov E and Gorkunov M 2003 Phys. Rev. Lett. 91 176602 | Origin of Stretched Exponential Relaxation for Hopping-Transport Models

| [28] | Gerrow K and Triller A 2010 Curr. Opin. Neurobiol. 20 631 | Synaptic stability and plasticity in a floating world